I2C vs SPI vs UART

- Get link

- X

- Other Apps

I2C VS SPI ALONG WITH UART COMPARISONS

shRAVAN TECHII

1.INTRODUCTION

Embedded systems rely on various protocols for effective data interaction. This article provides in-depth understanding and comprehensive comparison of three prominent protocols: Serial Peripheral Interface (SPI), Inter-Integrated Circuit (I2C), and Universal Asynchronous Receiver/Transmitter (UART). Each of these protocols serves distinct purposes and is characterized by unique specifications and operational principles. An understanding of these technologies is crucial for anyone involved in electronics design or embedded systems development, as these protocols often form the backbone of device communication within such systems. They enable the interaction between microcontrollers and various peripheral devices such as sensors, memory devices, and display modules, each with unique data transmission needs. By exploring their working principles, advantages, and disadvantages, you can make informed decisions when selecting the most suitable protocol for the specific use-cases.

2. What is SPI (Serial Peripheral Interface)?

SPI is a synchronous serial communication interface specification used for short-distance communication primarily in embedded systems. It facilitates full-duplex communication between a master device and one or multiple slave devices. The interface is notable for its simplicity and efficiency, making it a choice of interest for many embedded system designers.

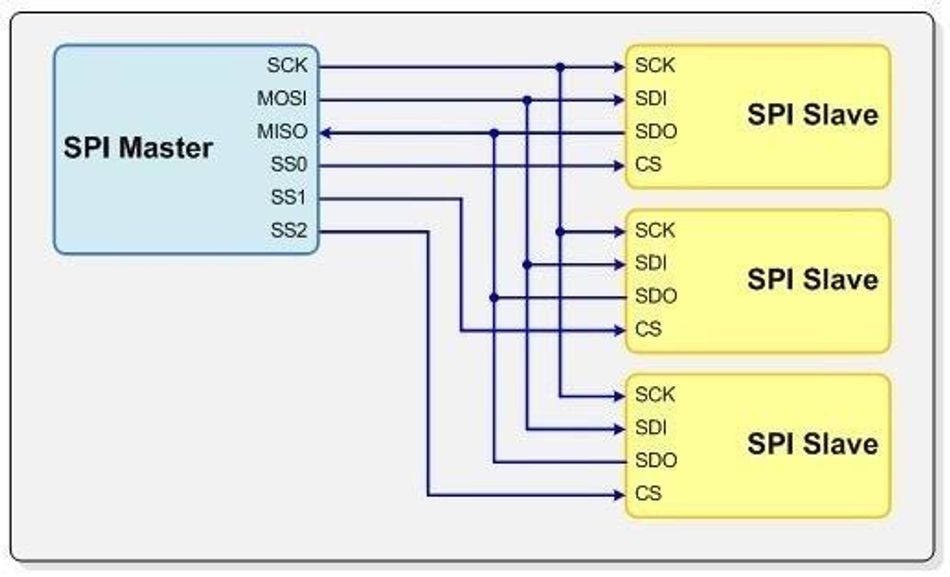

SPI is built on four fundamental lines: Master Out Slave In (MOSI), Master In Slave Out (MISO), Serial Clock (SCLK), and Slave Select (SS). The MOSI line carries data from the master device to the slave device, while the MISO line carries data in the opposite direction. The SCLK line, controlled by the master, paces the communication, while the SS line is used by the master to select which slave device it intends to communicate with.

2.1. Origin and Basic Principles

The SPI protocol was developed by Motorola in the mid-1980s, SPI was designed to provide a simple and efficient means of data exchange between microcontrollers and peripherals.

At its core, SPI communication relies on shifting data between Master and Salve, enabling full-duplex communication. Each transmission consists of at least two devices: a master device, which initiates and controls the communication, and a slave device, which responds to the master.

In a typical SPI transmission, the master generates a clock signal on the SCLK line and selects a slave device by setting its SS line to a low voltage level. The master and slave then exchange data simultaneously, with the master sending data to the slave on the MOSI line and the slave sending data to the master on the MISO line. The transmission continues for as many clock cycles as necessary, with the master finally ending the communication by returning the SS line of the selected slave to a high voltage level.

By controlling the clock signal and the SS line, the master can dictate the pace of communication and select which devices to interact with, making SPI an inherently flexible and efficient means of data exchange. However, it's worth noting that the lack of an in-built error-checking mechanism and the need for a dedicated SS line for each slave device are among the limitations of SPI that system designers need to consider.

2.2. SPI Communication Protocol

The SPI communication protocol revolves around synchronous data exchange, where data transfer is tied to a shared clock signal. The master generates the clock signal on the SCLK line, ensuring synchronized data transmission and reception. Data is shifted in and out on the MOSI and MISO lines, respectively, enabling simultaneous full-duplex communication.

To initiate communication, the master device selects a slave by driving its SS line low. The master then sends data to the slave on the MOSI line while simultaneously receiving data from the slave on the MISO line. This process continues for as many clock cycles as necessary, with the master terminating the communication by returning the SS line of the selected slave to a high voltage level.

The SPI communication speed depends on the clock frequency used. For example, a clock frequency of 4 MHz allows for a maximum data rate of 4 Mbps. This high data transfer rate makes SPI an excellent choice for applications requiring fast and efficient data exchange.

It is important to note that each slave device in an SPI system requires a dedicated SS line from the master. This limitation must be considered in resource-constrained environments where the number of available GPIO pins is limited.

Another consideration is that SPI lacks built-in error-checking mechanisms. Therefore, additional error checking and handling procedures may need to be implemented at the software level to ensure data integrity.

2.3. Advantages and Disadvantages of SPI

Understanding the advantages and disadvantages of SPI is crucial when evaluating its suitability for different applications. The following are the key points to consider:

2.3.1. Advantages of SPI:

SPI Include several advantages that make it a popular choice for communication in embedded systems. These advantages include|:

High-speed data transfer: With its synchronous communication mechanism, SPI enables fast and efficient data transfer, making it ideal for applications requiring high-speed communication. Compared to other serial communication protocols like UART and I2C, SPI offers significantly higher data transfer rates. For example, with a clock frequency of 10 MHz and 8 bits per transfer, the maximum data rate achievable would be 10 Mbps. This allows for quick exchange of data between the master and slave devices, enhancing overall system performance.

Full-duplex Communication: One of the key advantages of SPI is its ability to support simultaneous transmission and reception of data. While the master sends data to the slave on the Master Out Slave In (MOSI) line, it can receive data from the slave on the Master In Slave Out (MISO) line during the same clock cycle. This full-duplex capability is particularly advantageous in applications where real-time bidirectional data exchange is critical, such as in sensor interfacing or data acquisition systems.

Versatility and ease of implementation: SPI's simplicity and flexibility make it relatively easy to implement in various embedded systems. The interface can be integrated using dedicated hardware modules in microcontrollers or implemented in software, depending on the specific requirements of the application. Its straightforward design and well-defined communication protocol simplify the development process, reducing time and effort. Additionally, many microcontrollers provide built-in SPI peripherals, eliminating the need for additional external components.

Arbitrary data size: SPI does not impose restrictions on the size of data being transmitted. The master can continue shifting out data for as long as desired, allowing for transmission of data of arbitrary length. This feature is especially beneficial in scenarios where large amounts of data need to be transferred, such as in memory or display interfaces. Furthermore, SPI supports different data formats, including 8-bit, 16-bit, or even custom-defined data formats, providing flexibility to accommodate various data requirements.

Support for multiple slave devices: SPI allows for communication between one master device and multiple slave devices on the same bus. Each slave device is assigned a dedicated Slave Select (SS) line, which the master can control to select the desired slave for communication. This enables the system to interact with multiple peripherals, such as sensors, actuators, or memory chips, using a single SPI bus, simplifying system design and reducing the number of communication interfaces needed.

2.3.2. Disadvantages of SPI:

Despite its advantages, SPI also has some limitations and considerations that need to be taken into account. These include:

Lack of in-built error checking: One notable drawback of SPI is the absence of a built-in error checking mechanism. While its high-speed communication is a significant advantage, it also leaves room for potential data errors due to factors like signal noise, clock jitter, or voltage spikes. In systems where data integrity is crucial, additional error checking and handling procedures may need to be implemented at the software level. This can involve techniques like checksums, CRC (Cyclic Redundancy Check), or packet acknowledgment mechanisms to ensure reliable data transmission.

Limited scalability: As the number of devices increases in an SPI bus, the number of required Slave Select (SS) lines also increases since each slave device requires a dedicated SS line from the master. This can quickly exhaust the number of available General Purpose Input/Output (GPIO) pins in resource-constrained environments. Additionally, a higher number of devices can lead to increased power consumption and bus complexity. Therefore, when designing SPI-based systems, careful consideration must be given to the number of slave devices and available resources.

Unsuitable for long-distance communication: While SPI excels in short-distance communication within embedded systems, it is not well-suited for long-distance communication. As the speed increases and the distance grows, SPI becomes more susceptible to issues like signal degradation, electromagnetic interference, and timing problems. For long-distance communication, slower but more robust protocols like RS-485 or CAN are often preferred, as they are specifically designed to overcome these challenges.

Power consumption: In applications where power efficiency is critical, SPI may not be the most optimal choice. Unlike other communication protocols like I2C, SPI typically requires more power due to its synchronous nature and the need for additional SS lines for each slave device. This can be a concern in battery-operated devices or applications where minimizing power consumption is a priority. Careful power management techniques should be employed to mitigate this limitation, such as selectively enabling or disabling slave devices when not in use.

Suggested Readings: UART vs SPI: A Comprehensive Comparison for Embedded Systems

3. What is I2C (Inter-Integrated Circuit)?

The Inter-Integrated Circuit (I2C) is a synchronous serial communication protocol initially developed by Philips Semiconductor (now NXP Semiconductors) in the early 1980s. It is specifically designed for short-distance, intra-board communication between different components on the same circuit board, enabling the exchange of information. I2C utilizes a clock signal for synchronization purposes and offers unique features that allow multiple masters and slaves to coexist on a single communication setup, enabling flexible and complex architectures. The protocol utilizes two bidirectional open-drain lines known as the Serial Data Line (SDA) and the Serial Clock Line (SCL), which are pulled up with resistors and used by all devices on the I2C bus. Devices on the bus can act as senders (masters) or receivers (slaves).3.1. Origin and Basic Principles

The I2C protocol was developed in the 1980s by Philips Semiconductor as a simple intra-board communication solution, gaining widespread adoption due to its simplicity and efficiency. The acronym I2C stands for Inter-Integrated Circuit, emphasizing its purpose of facilitating communication between different integrated circuits (ICs) on the same board.

The fundamental principles of I2C communication revolve around the concepts of "masters" and "slaves." The master device initiates communication by providing the clock signal and controlling the overall transmission process, while the slave devices respond to the master's requests and participate in data exchange.

One notable aspect of I2C is its addressing system, wherein each device connected to the I2C bus has a unique address used by the master to communicate with it. This addressing scheme allows multiple devices to coexist on the bus without conflicts, promoting efficient and reliable communication.

I2C communication occurs over two wires: the Serial Data Line (SDA) and the Serial Clock Line (SCL). The SDA line is responsible for carrying data, while the SCL line provides the clock signal that synchronizes the data transfer. This setup simplifies the connection process and enables concurrent transmission and reception of data. Data transfer in I2C is bit-oriented, with each byte consisting of eight data bits.

Being a multi-master protocol, I2C allows multiple masters to be connected to the bus. This flexibility enables any master to initiate communication, making the protocol suitable for complex systems. Additionally, I2C incorporates bus arbitration and collision detection mechanisms to ensure orderly communication when multiple masters attempt to control the bus simultaneously. This robustness contributes to the versatility and reliability of I2C as a communication protocol.

3.2. I2C Communication Protocol

The I2C communication protocol follows a master-slave configuration, where one or more master devices control one or more slave devices. The master device provides the clock signal and initiates communication, while the slave devices respond to the master's requests and participate in data exchange. Communication in I2C is bidirectional, allowing both the master and the slave to transmit and receive data.

A distinguishing feature of I2C is its two-wire interface comprising the Serial Data Line (SDA) and the Serial Clock Line (SCL). The SDA line is responsible for data transfer, while the SCL line provides the clock signal, ensuring synchronization between devices. Both lines are bidirectional, allowing data to flow in both directions. They are open-drain, meaning devices can pull the line low (0 volts) to indicate a logical '0' or let it float high (up to a specified voltage, typically 3.3V or 5V) for a logical '1'. Pull-up resistors are necessary to ensure the lines return to the high state when no device is actively pulling them low.

In an I2C transaction, the master initiates the process by creating a START condition, pulling the SDA line low while the SCL line is high. This signal alerts all devices on the bus that a transmission is about to begin. The master then sends the 7 or 10-bit address of the slave device it wants to communicate with, accompanied by a bit indicating whether it intends to write to the slave (0) or read from it (1).

Upon receiving its address, the addressed slave acknowledges the receipt by pulling the SDA line low during the next clock pulse. Once the master receives this acknowledgment, it can proceed with sending or receiving data. Each byte of data is followed by an acknowledgment bit. When the master completes the transmission or reception of data, it generates a STOP condition, where it releases the SDA line to go high while the SCL line remains high.

To maintain the integrity of the bus, the I2C protocol incorporates error-checking measures. These include the use of acknowledgment bits and arbitration and collision detection mechanisms in multi-master systems. These features ensure smooth and reliable communication, even when multiple masters contend for control of the bus.

I2C supports different speed modes to accommodate various application requirements. Standard I2C devices typically support data rates up to 100K bits per second. Fast-mode devices extend this to 400K bits per second, while high-speed devices can achieve data rates of up to 3.4Mbits per second. These different speed modes enable I2C to cater to a wide range of devices, from slower, low-power components to faster, more complex devices.

3.3. Advantages and Disadvantages of I2C

3.3.1. Advantages of I2C

- Simplicity and Wire Efficiency: I2C offers a simple and efficient communication solution by using only two wires, SDA (Serial Data Line) and SCL (Serial Clock Line), irrespective of the number of devices on the bus. This simplicity reduces the complexity of circuit design, minimizes the number of connectors and traces on a PCB (Printed Circuit Board), and results in cost savings and compact system designs.

- Multi-Master and Multi-Slave Configuration: I2C supports multi-master and multi-slave configurations, allowing multiple master devices to communicate with multiple slave devices on the same bus. This flexibility enables the implementation of distributed processing architectures, where multiple microcontrollers, sensors, and other peripherals can seamlessly exchange data. It facilitates parallel communication channels and real-time data exchange within complex embedded systems.

- Addressing Scheme: I2C incorporates a built-in addressing scheme, enabling direct communication between the master and the designated slave devices without requiring additional wires for device selection. Each I2C device has a unique address, typically 7 or 10 bits long, allowing efficient data routing and eliminating the need for manual configuration or external decoding logic. The addressing scheme supports up to 128 (7-bit addressing) or 1024 (10-bit addressing) devices on a single bus.

- Speed Modes: I2C supports different speed modes to accommodate a wide range of devices and applications. The standard mode (up to 100K bits per second) suits slower peripherals and low-power components. Fast mode (up to 400K bits per second) enables faster data transfer, making it suitable for intermediate-speed devices. High-speed mode (up to 3.4Mbits per second) caters to high-performance applications that demand quick data exchange between devices. The selection of the appropriate speed mode depends on the specific requirements of the system.

- Synchronous Communication: I2C is a synchronous communication protocol, meaning it relies on a clock signal to synchronize data transfer between devices. The master device generates the clock signal, ensuring precise timing coordination. This synchronization allows for reliable and accurate data transmission, critical in applications where data integrity is paramount. The synchronous nature of I2C simplifies the design of communication interfaces and facilitates error detection and correction.

3.3.2. Disadvantages of I2C

- Distance Limitation: I2C is primarily designed for short-distance communication within a single circuit board or between closely located components. The capacitance of the bus and the resistance of the pull-up resistors limit the maximum achievable communication distance. As the length of the SDA and SCL lines increases, the total capacitance rises, resulting in slower rise times and potential signal degradation. For longer-distance communication, other protocols like UART (Universal Asynchronous Receiver/Transmitter) or SPI (Serial Peripheral Interface) may be more suitable.

- Speed Limitation: While I2C supports different speed modes, its high-speed mode (up to 3.4Mbits per second) may not match the data transfer rates of other protocols such as SPI. Applications requiring extremely high-speed communication might benefit from alternative protocols that offer faster data rates. However, it's important to consider the trade-offs between speed, complexity, and system requirements when selecting a communication protocol.

- Pull-up Resistors: I2C requires the use of pull-up resistors connected to the SDA and SCL lines. These resistors maintain the default high logic level on the bus. Selecting the appropriate resistor values is crucial to ensure reliable signal levels and proper bus operation. Insufficient or excessive resistor values can affect signal integrity and lead to communication errors. The calculation of pull-up resistor values depends on factors such as bus capacitance, desired rise times, and power supply voltage.

- Addressing Limitation: The I2C protocol supports a limited number of unique addresses, typically 7 or 10 bits long, which restricts the maximum number of devices that can be connected to a single bus. In scenarios with a high number of devices, addressing conflicts may arise, requiring additional measures such as address multiplexing or protocol converters to overcome the limitation. Careful planning and consideration of the device addressing scheme are essential to avoid conflicts and ensure successful communication.

- Clock Stretching: I2C allows slave devices to slow down the master's clock signal during data transfer through a mechanism called clock stretching. While clock stretching ensures synchronization and prevents data loss, it can introduce timing delays, impacting the overall system performance, especially in time-critical applications. Proper handling of clock stretching and understanding its implications on system timing is important for reliable I2C communication.Suggested Readings: I2C vs SPI protocols: differences, pros & cons, use cases (wevolver.com)

4. What is UART (Universal Asynchronous Receiver/Transmitter)?

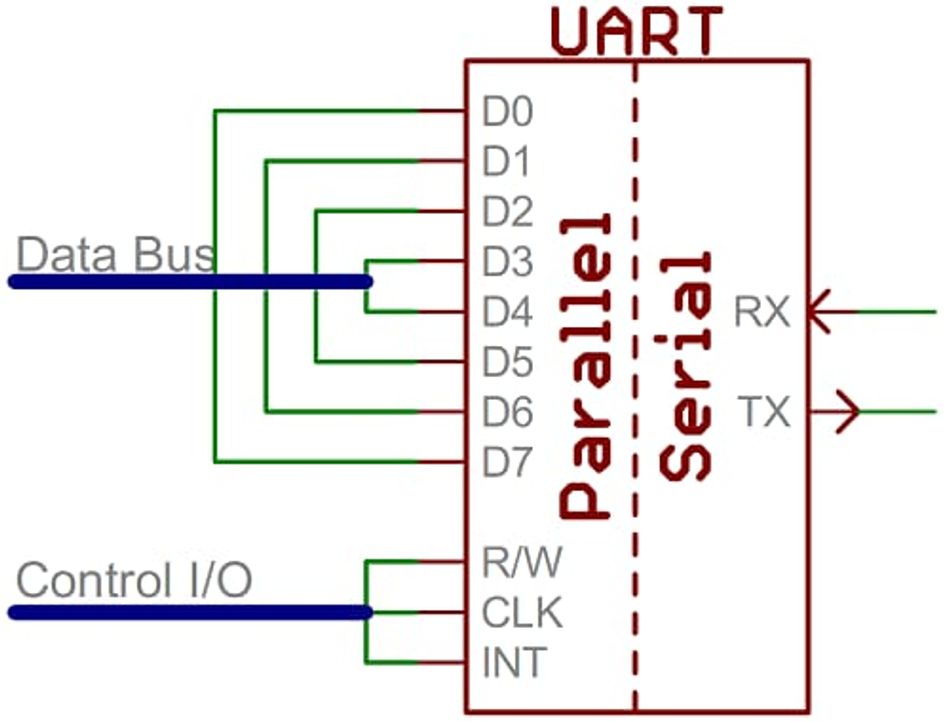

UART, short for Universal Asynchronous Receiver/Transmitter, is a fundamental hardware communication protocol extensively used for asynchronous serial communication. It serves as a vital interface between microcontrollers and peripheral devices, facilitating the exchange of data through serial transmission.

At its core, UART converts data bytes from the processor into a continuous stream of data bits, which are then transmitted serially over a single communication line. Similarly, incoming data is converted in reverse order for processing by the receiving device. Unlike synchronous communication protocols, UART does not rely on a shared clock signal for data synchronization.

Each data word transmitted via UART consists of various components. It begins with a start bit, which indicates the start of the data frame. The data bits follow the start bit and represent the actual information being transmitted. An optional parity bit can be included for error detection, enabling the receiver to identify and correct transmission errors. Finally, one or two stop bits mark the end of the data frame, providing the necessary time gap before the transmission of the next frame.

UARTs are ubiquitous in embedded systems, finding applications in diverse fields such as industrial automation, telecommunications, automotive electronics, and consumer electronics. They play a crucial role in enabling communication between microcontrollers and peripheral devices like sensors, displays, memory modules, and wireless transceivers.

4.1. Origin and Basic Principles

The origin of UART technology can be traced back to the early days of computing when standalone UART chips were developed in the 1960s. As integrated circuits advanced, UART functionality became integrated into microcontrollers and microprocessors, allowing for more compact and efficient implementations.

A UART operates based on the interaction between two shift registers: the Transmit Shift Register (TSR) and the Receive Shift Register (RSR). The process begins with the processor writing a byte of data into the Transmit Holding Register (THR). The data is then transferred to the Transmit Shift Register (TSR), where it undergoes serialization, converting it into a sequential stream of bits comprising the start, data, parity, and stop bits.

The serialized data is transmitted bit by bit through the Transmit Data (TXD) line at a speed determined by the Baud Rate Generator. The Baud Rate Generator, driven by a programmable clock source, sets the data transmission rate, commonly referred to as the baud rate. On the receiving end, the UART device captures the incoming bits from the Receive Data (RXD) line, performs deserialization within the Receive Shift Register (RSR), and stores the data byte in the Receive Buffer Register (RBR) for subsequent processing by the processor.

The hardware implementation of UART allows for efficient and autonomous data transfer, relieving the processor of the burden of handling low-level communication tasks. This asynchronous nature of UART communication enables the processor to focus on executing higher-level functions and enhances the overall performance and responsiveness of the system.

4.2. UART Communication Protocol

UART communication protocol is characterized by the transmission and reception of data through two dedicated lines: the Transmit (TX) line and the Receive (RX) line. Unlike synchronous communication protocols that rely on a shared clock signal, UART operates in an asynchronous mode, where both communicating devices must agree on the baud rate before initiating communication.

A UART data frame comprises several components. It starts with a start bit, which is always set to logic low (0) and serves as a signaling mechanism to indicate the beginning of the data frame. Following the start bit, the actual data bits are transmitted in a sequential manner, ranging from 5 to 9 bits depending on the configuration. An optional parity bit can be included for error detection and correction purposes. The parity bit allows the receiver to verify the integrity of the received data by checking for parity errors.

After the data bits, one or two stop bits mark the end of the data frame. These stop bits are always set to logic high (1) and provide a time gap between consecutive data frames, ensuring proper synchronization between the transmitter and receiver.

During data transmission, the UART transmitter pulls the transmission line from the idle state (logic high) to a start bit (logic low), indicating the start of a data frame. The receiver then reads the subsequent bits at the agreed-upon baud rate. Upon receiving the data bits, the receiver expects to encounter a stop bit set to logic high. If the received bit is not high, it indicates a transmission error.

One of the distinguishing features of UART communication is its full-duplex nature, enabling simultaneous transmission and reception of data. This is achieved through separate transmit and receive lines, allowing for bidirectional data flow. Additionally, UART communication protocol supports device-to-device communication, eliminating the need for a master-slave configuration and making it suitable for various applications.

With its simplicity, versatility, and wide adoption, UART remains a crucial communication protocol in the field of embedded systems and plays a pivotal role in enabling seamless data exchange between microcontrollers and peripheral devices.

4.3. Advantages and Disadvantages of UART

4.3.1. Advantages of UART

- Simple and Easy Implementation: UART communication is straightforward to implement, requiring only two wires for complete duplex data transfer (TX and RX lines). This simplicity makes the system setup simple and cost-effective, especially in resource-constrained embedded systems.

- Full Duplex Communication: UART enables simultaneous data reception and transmission, allowing for efficient utilization of the communication line. Both devices can send and receive data independently, without the need for explicit handshaking.

- Independent Operation: The absence of a clock signal simplifies wiring and allows devices to work independently, minimizing synchronization issues. Each device operates based on its internal clock, making UART well-suited for applications where devices have different clock sources or where clock synchronization is challenging.

- Support for Longer Data Frames: UART supports data frames with 5 to 9 data bits, providing flexibility to accommodate different data sizes in specific applications. This feature is particularly useful when dealing with non-standard data formats or when a larger number of bits are required for data representation.

- Point-to-Point Communication: UART facilitates direct communication between two devices without the need for a master or slave configuration. It allows for peer-to-peer communication, enabling devices to exchange data seamlessly without a central controlling unit. This makes UART suitable for applications such as wireless sensor networks or device interconnection.

4.3.2. Disadvantages of UART

- Synchronization Requirement: UART's asynchronous nature necessitates presetting the receiver and transmitter to the same baud rate for correct data transfer. This requirement may be impractical in scenarios with changing data rates or when devices operate at different clock speeds. In such cases, additional measures like dynamic baud rate adjustment or flow control protocols may be required.

- Potential Synchronization Issues: The absence of a dedicated clock line can lead to synchronization problems if there are variations in the system clock of the communicating devices. Clock drifts or inconsistencies in clock sources can cause timing errors and affect the accuracy of data transmission.

- Limited Error Detection: UART's error detection is limited to parity checking, which adds an extra bit to the data frame for error detection purposes. However, parity checking can only detect odd or even numbers of bit errors and is not as robust as more advanced error checking methods like cyclic redundancy check (CRC). This limitation may result in undetected errors, especially in environments prone to high levels of noise or interference.

- Lack of Addressing: UART does not inherently support addressing, making it challenging to natively accommodate multiple devices on the same bus. Without addressing, all devices on the bus receive the transmitted data, requiring additional mechanisms (e.g. software-based addressing) to distinguish and process the intended data.

- Limited Speed: UART's speed is limited by its design and implementation. While this limitation is not a concern for slow communication systems, it can be a significant constraint for high-speed applications. For example, a standard UART interface might support a maximum speed of 115200 bits per second (baud rate), which may not be sufficient for certain high-speed applications like real-time systems or high-speed data logging. In such cases, alternative communication protocols or higher-speed interfaces like SPI or Ethernet may be more appropriate.

5. Detailed Comparison: SPI vs I2C vs UART

5.1. Speed and Data Throughput

Speed

When comparing the raw data speed, SPI emerges as the fastest protocol among the three. It boasts clock speeds of up to 10 MHz and can achieve even higher speeds on certain microcontrollers. I2C follows, offering a standard mode operating speed of 100 kHz, a fast mode at 400 kHz, and a high-speed mode capable of reaching speeds up to 3.4 MHz. On the other hand, UART typically operates at speeds such as 9600, 19200, or 115200 bits per second (bps), making it the slowest of the three.

Data Throughput

Data throughput is influenced not only by speed but also by the efficiency with which that speed is utilized. SPI, being a full-duplex protocol, can send and receive data simultaneously, resulting in high efficiency. Additionally, since SPI does not utilize addressing, the overhead of transmitting address bytes is avoided, further enhancing throughput.

In comparison, I2C operates as a half-duplex protocol, incorporating address and acknowledge bits in its communication. This introduces additional overhead and reduces data throughput despite its decent clock speed. While I2C does support multi-master setups, the need for arbitration and collision detection can further diminish effective data throughput.

UART, similar to SPI, operates as a full-duplex protocol. However, it generally runs at slower speeds. Moreover, UART includes start and stop bits in each data frame to enable synchronization, which adds overhead and reduces the effective data throughput.

5.2. Power Consumption

Considering the power consumption of communication protocols is crucial in embedded systems, particularly in battery-powered applications.SPI's Power Consumption

SPI, with its high clock speed and full-duplex communication, often results in higher power consumption. Each data transmission involves clock pulses, and the higher the clock speed, the more power is consumed. Additionally, SPI requires multiple lines for communication, each of which contributes to power consumption. However, SPI does possess an advantage: it doesn't necessarily require pull-up resistors on the data and clock lines, unlike I2C, which can somewhat reduce power consumption. It is recommended to consult the datasheet of the specific SPI devices being used for detailed power consumption specifications.I2C's Power Consumption

I2C consumes less power than SPI due to its slower speed. Furthermore, its two-wire configuration requires fewer lines to be maintained, leading to lower static power consumption. However, the need for pull-up resistors on the data and clock lines in I2C can contribute to its power consumption. The power consumption of I2C varies depending on factors such as the value of the pull-up resistors and the bus capacitance. For precise power consumption figures, referring to the datasheet of the I2C devices is recommended.

UART's Power Consumption

UART's power consumption is typically lower than that of SPI and I2C, primarily due to its slower data rate. Fewer transitions per unit of time result in less dynamic power consumption. However, in idle mode, UART may consume more power as it maintains the line at a logical 'high' state. Nevertheless, many UART implementations include power-saving modes, such as sleep mode, which significantly reduce power consumption when the UART isn't actively transmitting. It is advised to refer to the datasheet of the specific UART devices for detailed power consumption information.5.3. Complexity and Ease of Implementation

The complexity of implementing a communication protocol in a system depends on various factors, including the number of devices to be connected, the need for error checking, the availability of hardware support, and the level of programming support

SPI's Complexity and Ease of Implementation

SPI implementation falls into the moderate complexity range. It requires four wires per device, which can make hardware design cumbersome, especially when multiple devices are involved. However, the absence of addressing makes the code implementation straightforward, as long as only one device is communicating at a time. It's worth noting that SPI generally requires more software control, particularly when handling multiple devices, as the microcontroller must manage individual chip select (CS) lines. Utilizing an Arduino or similar microcontroller can simplify the process through available libraries and example code provided by the community.

I2C's Complexity and Ease of Implementation

I2C strikes a balance between complexity and ease of implementation. Its two-wire interface simplifies hardware design, especially in setups involving multiple devices. However, its addressing scheme and the management of START and STOP conditions add complexity to the software side. Nonetheless, the built-in error checking features of I2C, such as acknowledge (ACK) bits and arbitration, can simplify the design of robust communication systems. Reference to the datasheet of the specific I2C devices and utilizing available I2C libraries for Arduino or other microcontrollers can aid in the implementation process.

UART's Complexity and Ease of Implementation

The UART interface is among the simplest to implement, making it an attractive choice for straightforward, point-to-point communications. The two-wire interface, consisting of transmit and receive lines, is simple to set up, and the lack of a clock signal simplifies timing concerns. However, UART lacks a built-in error-checking mechanism. Therefore, if error checking is required, additional software complexity must be considered. Additionally, multi-device communication isn't as straightforward with UART as it is with SPI and I2C, as it typically requires additional hardware or a complex software layer to implement. Reference to the datasheet of the specific UART devices and utilizing available UART libraries for Arduino or other microcontrollers can assist in the implementation process.

6. Practical Applications and Use-Cases

6.1. SPI Applications

Real-Time Systems

In real-time systems where low latency communication is critical, SPI's full-duplex, synchronous operation offers the desired performance. For instance, in digital signal processing applications, data often needs to be read from an analog-to-digital converter (ADC) while simultaneously writing to a digital-to-analog converter (DAC). The fast, concurrent data transmission and reception capabilities of SPI make it a suitable choice for such applications.

Furthermore, in real-time control systems, such as robotic systems or industrial automation, SPI can be used for high-speed communication between the central processing unit (CPU) and various peripherals. This allows for efficient exchange of sensor data, control signals, and actuator commands, enabling precise and timely system responses.

Data Streaming

SPI is also commonly employed in data streaming applications, especially in the field of multimedia and audio/video processing. One such example is the transmission of audio or video data to a codec. Given its high-speed data transfer rates, SPI can comfortably handle the streaming of high-bitrate data. A notable instance is the MP3 audio decoding in some media players, where the decoded audio data is sent from a microcontroller to a DAC using SPI.

Moreover, SPI's full-duplex nature allows for simultaneous data transmission and reception, making it suitable for real-time audio processing applications. For instance, in audio mixers or digital audio workstations, SPI can be used to exchange multiple audio channels between different processing modules or to interface with external audio interfaces.

SD Cards and LCDs

The SPI protocol is widely used in peripherals like SD cards and Liquid Crystal Display (LCD) modules. In the case of SD cards, SPI allows for high-speed data writing and reading, which is essential for applications that require large amounts of data storage. This is particularly relevant in IoT (Internet of Things) systems, where data logging and storage are crucial for capturing and analyzing sensor data.

Similarly, LCD modules often utilize SPI for fast data transfer to achieve quick screen refreshes, allowing for dynamic and responsive display updates. This is especially important in applications where real-time information display is required, such as in medical devices, industrial control panels, and consumer electronics.

6.2. I2C Applications

Sensor Integration

One of the primary applications of I2C is the integration of various sensors in systems. Sensors typically output data at a relatively low rate, so I2C's speed is more than sufficient. For instance, temperature sensors, humidity sensors, or accelerometers in a weather station or a wearable device often employ I2C for data transmission to the microcontroller. This simplifies design as only two wires are required to connect multiple sensors.

Moreover, I2C's support for multi-master configurations enables efficient communication between sensors and the central processing unit (CPU) in complex IoT systems. The CPU can access sensor data from multiple I2C devices by sequentially addressing them and retrieving the required information, enabling comprehensive environmental monitoring and control.

Low-Speed Peripheral Devices

The I2C protocol is frequently used for interfacing low-speed peripheral devices that require reliable communication with the microcontroller. These devices can include digital potentiometers, EEPROMs, real-time clocks, and various types of sensors. For example, a digital potentiometer connected via I2C can be used to control the volume in an audio amplifier. In this case, the speed of I2C (up to 400kHz or 1MHz in fast-mode plus) is adequate for the purpose, and the ease of connecting multiple devices on the same bus is a significant advantage.

Additionally, I2C's support for clock stretching allows peripheral devices to slow down the bus temporarily if they need more time to process data or complete an operation. This feature ensures reliable and synchronized communication between the microcontroller and peripheral devices, enhancing the overall system performance and stability.

Onboard Communication

I2C is also a common choice for onboard communication between different components of a device, such as communication between different ICs on a motherboard or within an embedded system. In such scenarios, the short distances between components make the relatively low speed of I2C less of a concern, while its ability to connect multiple devices with only two bus lines provides a significant advantage in terms of reducing wiring complexity.

For example, in a complex IoT device or a smart home automation system, I2C can be used to establish communication between microcontrollers, sensors, actuators, and display modules. This enables seamless data exchange and coordination among different subsystems, facilitating efficient control, monitoring, and user interaction.

6.3. UART Applications

GPS Receivers

UART is widely used in communication with GPS receivers. GPS modules often output location information at a low baud rate that is compatible with UART's communication speed. A system with a GPS module would typically use UART to receive location data, perform necessary calculations or processing, and perhaps send configuration data to the GPS module. The simple point-to-point nature of UART communication, and the fact that it doesn't require clock synchronization, is well-suited to this type of application.

Furthermore, UART's flexibility allows for easy integration with other navigation-related sensors, such as compasses or gyroscopes, to provide comprehensive positioning and orientation information for applications like vehicle tracking, navigation systems, and unmanned aerial vehicles (UAVs).

Microcontroller to Microcontroller Communication

UART is also commonly used for communication between two microcontrollers. If two devices need to exchange a moderate amount of data and they're reasonably close to each other, UART is a reliable choice. The absence of a clock line can simplify circuit design and potentially save on hardware resources. UART can either directly connect the two microcontrollers or establish a connection using a wireless module such as Bluetooth.

In complex systems, where multiple microcontrollers need to collaborate and share data, UART can be utilized as an intercommunication channel, enabling synchronization, task distribution, and data exchange between different units. This is often seen in distributed control systems, robotics, and IoT applications where seamless coordination among multiple processing units is required.

Debugging and Diagnostic Ports

In many embedded systems, UART is used as a debugging port. Engineers use these ports to print debug information, check the status of various system components, and perform other diagnostic tasks. For instance, in the booting process of an embedded device, valuable information about the system's status is printed to a UART console. The slower data rates and simple communication protocol are sufficient for this purpose, and the lack of a need for an additional clock signal or synchronization is a plus for system developers.

UART's role as a debugging and diagnostic port extends beyond the initial development phase. It allows for real-time monitoring of system behavior, identification of potential issues or errors, and provides an interface for firmware updates or configuration changes. This helps in maintaining and troubleshooting embedded systems throughout their operational lifespan.

PC Peripherals

The legacy of UART as a PC interface persists in many modern devices. It can be found in older mice, keyboards, and even printers. In addition, some modern peripherals that interface with PCs, like certain types of sensors or development boards, may use UART for communication, either natively or through a USB-to-UART bridge. It provides a simple and reliable communication mechanism that can be easily implemented with minimal overhead.

UART's compatibility with PCs and its standardized interface make it a convenient choice for connecting various peripheral devices to computers. From input devices like mice and keyboards to output devices like displays and printers, UART allows for seamless data transmission and control, ensuring reliable and efficient interaction between the user and the computer system.

7. Choosing the Right Protocol: SPI vs I2C vs UART Speed Requirement and Data Transmission Speed

The speed requirement of the device is a critical factor when selecting a communication protocol. SPI stands out in terms of high-speed data transfer, with data rates typically reaching 10 MHz or even higher. This makes SPI ideal for applications that demand rapid and efficient data transmission. On the other hand, UART is better suited for lower-speed applications, with typical data rates around 115200 bps. UART's data transmission speed makes it suitable for scenarios where moderate amounts of data need to be exchanged. I2C falls in between, offering a maximum data rate of 3.4 Mbps in its high-speed mode. While not as fast as SPI, I2C's data transmission speed is still sufficient for many applications.

Data Integrity and Error Detection

Ensuring data integrity is crucial in communication protocols. SPI, although lacking an inherent error checking mechanism, provides immediate feedback through its full-duplex communication mode. This allows the receiving device to verify the accuracy of the transmitted data. In contrast, both I2C and UART have built-in error detection mechanisms. I2C employs acknowledgment bits to confirm the receipt of each byte, providing a reliable means of ensuring data integrity. UART uses a parity bit for error detection, allowing the receiving device to detect and correct errors during data transmission.

Number of Devices and Multi-Master vs Single-Master

The number of devices that can be connected to a communication bus is an important consideration. I2C supports multiple devices on the bus, each with a unique address. This makes I2C well-suited for applications where multiple sensors or peripherals need to communicate with a central microcontroller. SPI can also accommodate multiple devices by using separate Slave Select lines for each device, allowing for communication with individual devices as needed. However, as the number of devices increases, managing the dedicated Slave Select lines can become challenging, leading to scalability issues. UART, being a point-to-point communication protocol, does not inherently support multiple devices without additional hardware or software management. It is primarily designed for direct communication between two devices.

Power Consumption and Power Efficiency

Power consumption is a critical consideration, especially in low-power applications or battery-operated devices. I2C, with its open-drain bus architecture, requires pull-up resistors to maintain signal integrity. This can potentially result in higher power consumption compared to SPI or UART. However, it is important to note that the power consumption of a communication protocol also depends on other factors, such as the operating frequency and the data transfer rate. In high data rate applications, SPI may consume more power due to its higher clock frequency. Therefore, it is essential to consider the specific requirements and constraints of the application when evaluating power efficiency.

Ease of Implementation and Hardware Resources

The ease of implementing a communication protocol is another crucial factor. UART is relatively simpler to implement as it does not require a dedicated clock line. However, the lack of a standardized communication protocol can complicate software design, especially when establishing communication between devices from different manufacturers. SPI requires more pins for communication, typically utilizing separate lines for master output, master input, and slave output. Despite the additional pins, SPI provides a straightforward and efficient data transfer mechanism, making it easier to implement. I2C requires fewer lines for communication and offers the advantage of addressing multiple devices on the bus. However, the need for unique addresses and the complexity of the I2C protocol can introduce challenges during implementation. Additionally, the availability and capabilities of communication peripherals on the microcontroller or microprocessor being used should be considered, as not all devices support all three protocols.

The selection of the appropriate communication protocol, whether it is SPI, I2C, or UART, depends on various factors, including the required data transmission speed, data integrity needs, the number of devices to be connected, power consumption constraints, ease of implementation, and the available hardware resources. By carefully evaluating these factors, designers can determine the most suitable protocol that aligns with the specific requirements of their application.

8. Conclusion

The communication protocols SPI, I2C, and UART play vital roles in the operation of embedded systems. Understanding the strengths and weaknesses of these protocols is essential when designing systems that require efficient data exchange between components. SPI excels in high-speed communication, making it suitable for applications where fast and concurrent data transmission is critical. I2C offers the advantage of addressing multiple devices with fewer resources, providing flexibility in system design. UART stands out when point-to-point communication is needed, particularly over longer distances where reliable data transfer is essential.

10. Frequently Asked Questions (FAQs)

Q1: How does SPI handle communication with multiple slave devices?

In SPI, communication with multiple slave devices is managed through individual Slave Select (SS) lines. Each slave device connected to the SPI bus has its dedicated SS line. The master device selects a particular slave by pulling its SS line low, enabling data exchange with that specific slave.

Q2: Can I2C and SPI work together in the same system?

Yes, I2C and SPI can coexist in the same system as they operate independently of each other. It is possible to use I2C for certain components while utilizing SPI for others. However, careful management of the shared bus lines is required to avoid conflicts and ensure proper communication between the devices.

Q3: Why does UART not need a clock line?

UART does not require a dedicated clock line because it is an asynchronous communication protocol. Instead of relying on a shared clock signal, the transmitting and receiving devices agree on a predetermined baud rate for data transmission. Each data byte is framed by start and stop bits, allowing the receiving device to identify and interpret the incoming data.

Q4: Why is SPI faster than I2C and UART?

SPI achieves higher data transfer rates compared to I2C and UART due to several factors. Firstly, SPI does not carry addressing information in its data frames, resulting in more efficient use of bandwidth. Secondly, SPI operates in full-duplex mode, enabling simultaneous data transmission and reception. Additionally, the clock speed used in SPI is generally higher than that of I2C and UART, further contributing to its faster performance.

Q5: How does I2C handle collisions on the bus?

I2C incorporates a collision-handling mechanism to resolve conflicts on the bus. If two devices start transmitting simultaneously, a collision occurs. In such cases, the device transmitting a '1' while the other transmits a '0' will lose arbitration. The losing device detects the collision and immediately stops transmitting, allowing the winning device to continue communication uninterrupted.

- Get link

- X

- Other Apps

Good

ReplyDelete